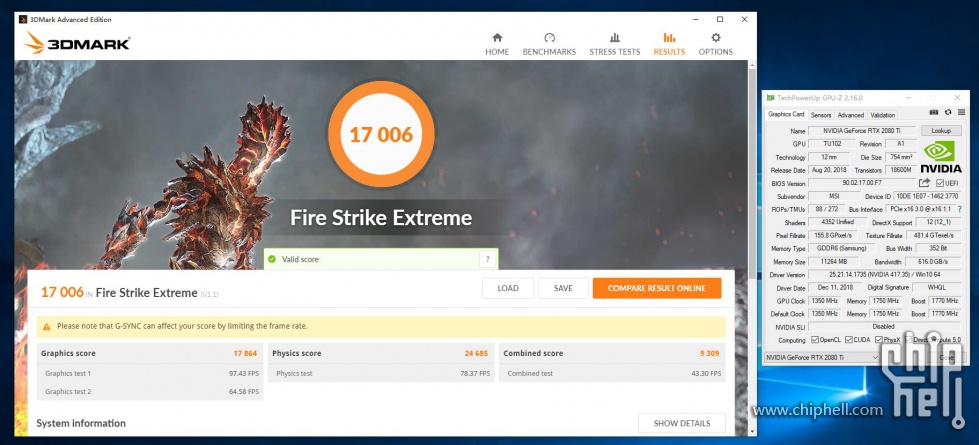

2115 core/1200 mem, 实际运行的core应该在2050左右

https://www.3dmark.com/fs/18271233

Capture.PNG (261.31 KB, 下载次数: 0)

使用A卡独门绝技关闭曲面细分之后:

https://www.3dmark.com/fs/18271271

Capturetess.PNG (262.58 KB, 下载次数: 0)

评论

不愧是苏妈特挑的苏7.。。。其他都是雷7

评论

这是特挑版的吧?普通玩家根本买不到。

评论

妮这是RMA了多少张换来的?

评论

这是苏7! 其他都是雷7!

评论

估计是5000张。

评论

重复了。

评论

测一下trinoline的帧数哎!

评论

苏卡不雷!

评论

摸到2080ti的

评论

你这卡怕不是用最好的晶圆取最好的部分用状态最好的机器弄出来的

评论

苏妈怕5000张全被你RMA过,干脆直接给片大雕你了

评论

没有参考价值

评论

现在又没开卖,她用的苏妈的戒指卡。

评论

思思是谁

评论

这分赶上2080ti了吧

评论

这个有点意思

逗.PNG (90.95 KB, 下载次数: 0)

评论

比2080高点,和2080ti差很远

评论

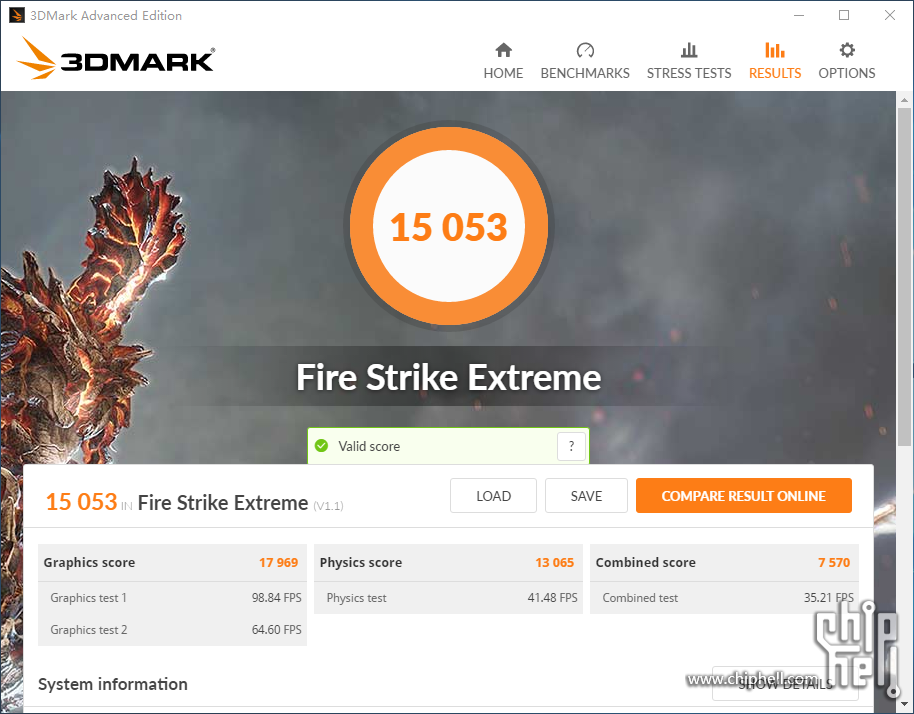

MSI GeForce RTX 2080 Ti Lightning Z 评测中3DMark Fire Strike Extreme显卡分数17969,总分15053.

评论

真 · 快摸到 2080Ti 了……

评论

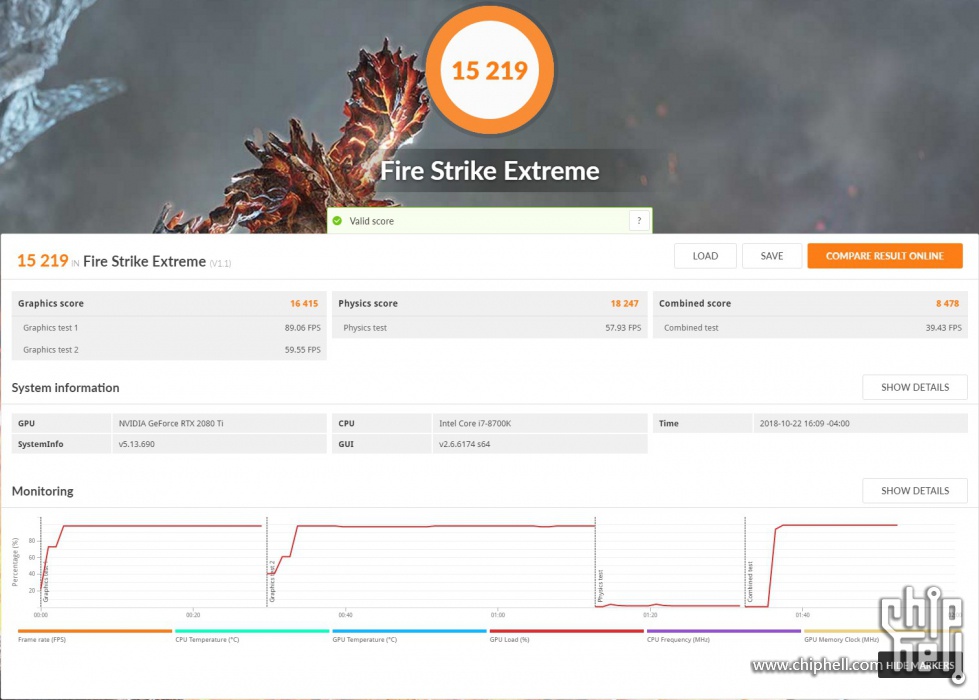

RTX 2080Ti FE的评测中3DMark Fire Strike Extreme显卡分数16415,总分15219

评论

敢问拉了多少功耗上限 电压1218mV加满了?

评论

FSE衡量图灵卡的性能偏低

评论

果然这楼主是爱你哦…?

评论

不是妳啦,别紧张。

评论

280%

Windows Registry Editor Version 5.00

[HKEY_LOCAL_MACHINE\SYSTEM\CurrentControlSet\Control\Class\{4d36e968-e325-11ce-bfc1-08002be10318}\0000]

"PP_PhmSoftPowerPlayTable"=hex:C2,06,0B,00,02,C2,06,34,08,00,00,A4,35,00,00,7C,00,09,00,00,00,1A,FA,\

00,FA,00,FA,00,00,00,00,00,76,00,01,0B,00,00,00,09,07,00,00,6E,04,00,00,CC,03,00,00,CC,03,00,00,CC,\

03,00,00,E8,03,00,00,C9,04,00,00,6E,04,00,00,6E,04,00,00,34,04,00,00,2A,03,00,00,00,00,00,00,00,00,\

00,00,00,00,00,00,00,00,00,00,00,00,00,00,BC,02,00,00,66,01,00,00,36,01,00,00,36,01,00,00,36,01,00,\

00,5E,01,00,00,26,02,00,00,66,01,00,00,66,01,00,00,93,00,00,00,0E,01,00,00,00,00,00,00,00,00,00,00,\

00,00,00,00,00,00,00,00,00,00,00,00,01,0E,00,00,00,01,01,01,01,01,01,01,01,01,00,01,01,01,01,00,00,\

00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,1D,00,00,00,98,08,00,00,98,08,00,00,98,08,00,00,C2,\

04,00,00,98,08,00,00,C2,04,00,00,98,08,00,00,C2,04,00,00,B0,04,00,00,14,00,00,00,0A,0F,00,00,0A,0F,\

00,00,5F,00,00,00,6E,00,00,00,02,00,00,00,00,00,00,00,01,00,00,00,01,00,00,00,01,00,00,00,5F,00,00,\

00,64,00,00,00,5F,00,00,00,64,00,00,00,5F,00,00,00,64,00,00,00,5F,00,00,00,64,00,00,00,5F,00,00,00,\

64,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,28,03,00,00,28,03,00,00,28,03,00,00,E2,02,00,00,28,\

03,00,00,E2,02,00,00,28,03,00,00,E2,02,00,00,5E,01,00,00,14,00,00,00,C2,01,00,00,C2,01,00,00,19,00,\

00,00,32,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,19,00,00,00,14,00,00,\

00,19,00,00,00,14,00,00,00,19,00,00,00,14,00,00,00,19,00,00,00,14,00,00,00,19,00,00,00,14,00,00,00,\

00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,03,00,00,00,FF,EF,F4,39,00,00,00,\

00,BC,02,00,00,00,00,00,00,00,00,00,00,00,00,00,00,BC,02,00,00,32,00,00,00,BC,02,00,00,64,00,6E,00,\

5E,00,73,00,73,00,FF,FF,FF,FF,FF,FF,00,00,00,00,00,00,00,00,01,00,73,00,00,00,00,00,00,00,00,00,86,\

0B,22,0B,0B,13,43,12,26,00,00,00,01,01,09,00,00,00,00,00,00,00,00,00,5B,B1,BF,3E,EC,51,F8,BE,65,19,\

52,3F,00,01,08,00,64,3B,9F,3F,16,DE,A5,BD,00,00,00,00,00,00,00,00,00,00,00,00,00,01,08,00,35,5E,9A,\

3F,8F,36,2E,3E,00,00,00,00,00,00,00,00,00,00,00,00,00,01,08,00,69,6F,B0,3F,48,33,16,3D,00,00,00,00,\

00,00,00,00,00,00,00,00,00,01,08,00,E5,61,A1,3F,12,F7,58,BD,00,00,00,00,00,00,00,00,00,00,00,00,00,\

01,03,00,B5,15,83,3F,C2,DD,19,3E,00,00,00,00,00,00,00,00,00,00,00,00,00,01,08,00,86,38,86,3F,0E,BE,\

30,3E,00,00,00,00,00,00,00,00,00,00,00,00,00,01,08,00,83,C0,5A,3F,4D,A1,F3,3D,00,00,00,00,00,00,00,\

00,00,00,00,00,02,01,08,00,00,00,00,00,00,00,00,00,A4,70,8D,3F,E4,14,85,BF,D5,E7,32,3F,02,01,03,00,\

00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,D5,E7,32,3F,01,01,08,00,00,00,80,3F,00,00,00,00,D1,\

91,FC,3E,1F,85,2B,BF,32,77,75,3F,BC,02,28,03,6E,04,5C,05,0A,06,93,06,D5,06,ED,06,09,07,00,00,00,00,\

00,00,00,00,00,00,00,00,00,00,66,01,E6,01,6B,02,F4,02,52,03,CC,03,6E,04,6E,04,36,01,90,01,0C,02,6B,\

02,A8,02,F4,02,52,03,CC,03,36,01,90,01,0C,02,6B,02,A8,02,F4,02,52,03,CC,03,36,01,0C,02,37,02,6B,02,\

A8,02,F4,02,52,03,CC,03,5E,01,20,03,E8,03,E8,03,26,02,62,02,B2,02,F8,02,66,03,C0,03,38,04,C9,04,66,\

01,C6,01,37,02,A8,02,F4,02,52,03,CC,03,6E,04,66,01,C6,01,37,02,A8,02,F4,02,52,03,CC,03,6E,04,93,00,\

F2,00,58,01,E4,01,15,02,AA,03,13,04,34,04,0E,01,1C,02,2A,03,00,00,00,00,00,00,00,00,00,00,09,07,6E,\

04,CC,03,CC,03,CC,03,E8,03,6E,04,6E,04,34,04,2A,03,C9,04,00,00,C8,00,2C,01,60,09,F0,0A,28,03,00,00,\

00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,09,07,01,00,00,00,00,00,00,02,06,06,50,\

00,34,01,00,00,00,00,00,00,00,00,00,00,00,00,90,01,90,01,90,01,90,01,90,01,90,01,90,01,14,00,54,0B,\

54,0B,0A,0F,5F,00,00,00,00,02,00,00,00,00,00,00,00,00,00,01,00,00,00,00,00,00,50,8D,97,3C,0A,D7,A3,\

3B,00,00,00,00,EA,B2,98,3C,87,A2,40,3D,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,\

00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,\

00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,\

00,00,00,00,A0,00,01,00,00,00,00,00,00,00,A0,00,00,00,08,10,02,10,1A,04,4C,04,E8,03,E8,03,E8,03,E8,\

03,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,\

00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,86,0B,22,0B,54,0B,00,00,90,\

01,90,01,38,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,\

00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,\

00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,\

00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,\

00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,\

00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,\

00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,\

00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,\

00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,\

00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,\

00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,\

00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00,00

评论

才不像妳那样天天RMA。这卡路边捡到的,人家很有信仰,所以就跑的分高囖~

评论

我惊了

评论

注册表软BIOS专治什么人软件不服

可惜人家看不懂这些数据啊英文啊,只会下载大佬们的文件导入而已。毛毛你会弄的话,这里面频率电压功耗啥都随便改。16000应该是新常态!

https://www.overclock.net/forum/ ... 4.html#post27846710

typedef struct _ATOM_VEGA20_POWERPLAYTABLE

{

struct atom_common_table_header sHeader;

{

C2 06 USHORT usStructureSize;

0B UCHAR ucTableFormatRevision; /*Change it when the Parser is not backward compatible */

00 UCHAR ucTableContentRevision; /*Change it only when the table needs to change but the firmware */

/*Image can't be updated, while Driver needs to carry the new table! */

} ATOM_COMMON_TABLE_HEADER;

02 UCHAR ucTableRevision;

C2 06 USHORT usTableSize;

34 08 00 00 ULONG ulGoldenPPID;

A4 35 00 00 ULONG ulGoldenRevision;

7C 00 USHORT usFormatID;

09 00 00 00 ULONG ulPlatformCaps;

1A UCHAR ucThermalControllerType;

FA 00 (250W) USHORT usSmallPowerLimit1;

FA 00 (250W) USHORT usSmallPowerLimit2;

FA 00 (250W) USHORT usBoostPowerLimit;

00 00 USHORT usODTurboPowerLimit;

00 00 USHORT usODPowerSavePowerLimit;

76 00 (118°C) USHORT usSoftwareShutdownTemp;

ATOM_VEGA20_POWER_SAVING_CLOCK_RECORD PowerSavingClockTable; //PowerSavingClock Mode Clock Min/Max array

typedef struct _ATOM_VEGA20_POWER_SAVING_CLOCK_RECORD

{

01 UCHAR ucTableRevision;

0B 00 00 00 ULONG PowerSavingClockCount; // Count of PowerSavingClock Mode

ULONG PowerSavingClockMax [16]; // PowerSavingClock Mode Clock Maximum array In MHz

09 07 00 00

6E 04 00 00

CC 03 00 00

CC 03 00 00

CC 03 00 00

E8 03 00 00

C9 04 00 00

6E 04 00 00

6E 04 00 00

34 04 00 00

2A 03 00 00

00 00 00 00

00 00 00 00

00 00 00 00

00 00 00 00

00 00 00 00

ULONG PowerSavingClockMin [16]; // PowerSavingClock Mode Clock Minimum array In MHz

BC 02 00 00

66 01 00 00

36 01 00 00

36 01 00 00

36 01 00 00

5E 01 00 00

26 02 00 00

66 01 00 00

66 01 00 00

93 00 00 00

0E 01 00 00

00 00 00 00

00 00 00 00

00 00 00 00

00 00 00 00

00 00 00 00

} ATOM_VEGA20_POWER_SAVING_CLOCK_RECORD;

ATOM_VEGA20_OVERDRIVE8_RECORD OverDrive8Table; //OverDrive8 Feature capabilities and Settings Range (Max and Min)

typedef struct _ATOM_VEGA20_OVERDRIVE8_RECORD

{

01 UCHAR ucODTableRevision;

0E 00 00 00 ULONG ODFeatureCount;

UCHAR ODFeatureCapabilities [32]; //OD feature support flags

01

01

01

01

01

01

01

01

01

00

01

01

01

01

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

1D 00 00 00 ULONG ODSettingCount;

ULONG ODSettingsMax [32]; //Upper Limit for each OD Setting

98 08 00 00

98 08 00 00

98 08 00 00

C2 04 00 00

98 08 00 00

C2 04 00 00

98 08 00 00

C2 04 00 00

B0 04 00 00

14 00 00 00

0A 0F 00 00

0A 0F 00 00

5F 00 00 00

6E 00 00 00

02 00 00 00

00 00 00 00

01 00 00 00

01 00 00 00

01 00 00 00

5F 00 00 00

64 00 00 00

5F 00 00 00

64 00 00 00

5F 00 00 00

64 00 00 00

5F 00 00 00

64 00 00 00

5F 00 00 00

64 00 00 00

00 00 00 00

00 00 00 00

00 00 00 00

ULONG ODSettingsMin [32]; //Lower Limit for each OD Setting

28 03 00 00

28 03 00 00

28 03 00 00

E2 02 00 00

28 03 00 00

E2 02 00 00

28 03 00 00

E2 02 00 00

5E 01 00 00

14 00 00 00

C2 01 00 00

C2 01 00 00

19 00 00 00

32 00 00 00

00 00 00 00

00 00 00 00

00 00 00 00

00 00 00 00

00 00 00 00

19 00 00 00

14 00 00 00

19 00 00 00

14 00 00 00

19 00 00 00

14 00 00 00

19 00 00 00

14 00 00 00

19 00 00 00

14 00 00 00

00 00 00 00

00 00 00 00

00 00 00 00

} ATOM_VEGA20_OVERDRIVE8_RECORD;

USHORT usReserve[5];

00 00

00 00

00 00

00 00

00 00

PPTable_t smcPPTable;

} ATOM_Vega20_POWERPLAYTABLE;

enum ATOM_VEGA20_ODFEATURE_ID {

ATOM_VEGA20_ODFEATURE_GFXCLK_LIMITS = 0,

ATOM_VEGA20_ODFEATURE_GFXCLK_CURVE,

ATOM_VEGA20_ODFEATURE_UCLK_MAX,

ATOM_VEGA20_ODFEATURE_POWER_LIMIT,

ATOM_VEGA20_ODFEATURE_FAN_ACOUSTIC_LIMIT, //FanMaximumRpm

ATOM_VEGA20_ODFEATURE_FAN_SPEED_MIN, //FanMinimumPwm

ATOM_VEGA20_ODFEATURE_TEMPERATURE_FAN, //FanTargetTemperature

ATOM_VEGA20_ODFEATURE_TEMPERATURE_SYSTEM, //MaxOpTemp

ATOM_VEGA20_ODFEATURE_MEMORY_TIMING_TUNE,

ATOM_VEGA20_ODFEATURE_FAN_ZERO_RPM_CONTROL,

ATOM_VEGA20_ODFEATURE_COUNT,

};

enum ATOM_VEGA20_ODSETTING_ID {

ATOM_VEGA20_ODSETTING_GFXCLKFMAX = 0,

ATOM_VEGA20_ODSETTING_GFXCLKFMIN,

ATOM_VEGA20_ODSETTING_VDDGFXCURVEFREQ_P1,

ATOM_VEGA20_ODSETTING_VDDGFXCURVEVOLTAGEOFFSET_P1,

ATOM_VEGA20_ODSETTING_VDDGFXCURVEFREQ_P2,

ATOM_VEGA20_ODSETTING_VDDGFXCURVEVOLTAGEOFFSET_P2,

ATOM_VEGA20_ODSETTING_VDDGFXCURVEFREQ_P3,

ATOM_VEGA20_ODSETTING_VDDGFXCURVEVOLTAGEOFFSET_P3,

ATOM_VEGA20_ODSETTING_UCLKFMAX,

ATOM_VEGA20_ODSETTING_POWERPERCENTAGE,

ATOM_VEGA20_ODSETTING_FANRPMMIN,

ATOM_VEGA20_ODSETTING_FANRPMACOUSTICLIMIT,

ATOM_VEGA20_ODSETTING_FANTARGETTEMPERATURE,

ATOM_VEGA20_ODSETTING_OPERATINGTEMPMAX,

ATOM_VEGA20_ODSETTING_COUNT,

};

typedef enum ATOM_VEGA20_ODSETTING_ID ATOM_VEGA20_ODSETTING_ID;

enum ATOM_VEGA20_PPCLOCK_ID {

ATOM_VEGA20_PPCLOCK_GFXCLK = 0,

ATOM_VEGA20_PPCLOCK_VCLK,

ATOM_VEGA20_PPCLOCK_DCLK,

ATOM_VEGA20_PPCLOCK_ECLK,

ATOM_VEGA20_PPCLOCK_SOCCLK,

ATOM_VEGA20_PPCLOCK_UCLK,

ATOM_VEGA20_PPCLOCK_FCLK,

ATOM_VEGA20_PPCLOCK_DCEFCLK,

ATOM_VEGA20_PPCLOCK_DISPCLK,

ATOM_VEGA20_PPCLOCK_PIXCLK,

ATOM_VEGA20_PPCLOCK_PHYCLK,

ATOM_VEGA20_PPCLOCK_COUNT,

};

typedef enum ATOM_VEGA20_PPCLOCK_ID ATOM_VEGA20_PPCLOCK_ID;

00 00 FanStopTemp

00 00 FanStartTemp

90 01 FanGainEdge

90 01 FanGainHotspot

90 01 FanGainLiquid

90 01 FanGainVrGfx

90 01 FanGainVrSoc

90 01 FanGainPlx

90 01 FanGainHbm

14 00 FanPwmMin

54 0B FanAcousticLimitRpm

54 0B FanThrottlingRpm

0A 0F FanMaximumRpm

5F 00 FanTargetTemperature

00 00 FanTargetGfxclk

00 FanZeroRpmEnable

02 FanTachEdgePerRev

00 00 FuzzyFan_ErrorSetDelta

00 00 FuzzyFan_ErrorRateSetDelta

00 00 FuzzyFan_PwmSetDelta

00 00 FuzzyFan_Reserved

typedef struct {

uint32_t Version;

uint32_t FeaturesToRun[2];

uint16_t SocketPowerLimitAc0;

uint16_t SocketPowerLimitAc0Tau;

uint16_t SocketPowerLimitAc1;

uint16_t SocketPowerLimitAc1Tau;

uint16_t SocketPowerLimitAc2;

uint16_t SocketPowerLimitAc2Tau;

uint16_t SocketPowerLimitAc3;

uint16_t SocketPowerLimitAc3Tau;

uint16_t SocketPowerLimitDc;

uint16_t SocketPowerLimitDcTau;

uint16_t TdcLimitSoc;

uint16_t TdcLimitSocTau;

uint16_t TdcLimitGfx;

uint16_t TdcLimitGfxTau;

uint16_t TedgeLimit;

uint16_t ThotspotLimit;

uint16_t ThbmLimit;

uint16_t Tvr_gfxLimit;

uint16_t Tvr_memLimit;

uint16_t Tliquid1Limit;

uint16_t Tliquid2Limit;

uint16_t TplxLimit;

uint32_t FitLimit;

uint16_t PpmPowerLimit;

uint16_t PpmTemperatureThreshold;

uint8_t MemoryOnPackage;

uint8_t padding8_limits;

uint16_t Tvr_SocLimit;

uint16_t UlvVoltageOffsetSoc;

uint16_t UlvVoltageOffsetGfx;

uint8_t UlvSmnclkDid;

uint8_t UlvMp1clkDid;

uint8_t UlvGfxclkBypass;

uint8_t Padding234;

uint16_t MinVoltageGfx;

uint16_t MinVoltageSoc;

uint16_t MaxVoltageGfx;

uint16_t MaxVoltageSoc;

uint16_t LoadLineResistanceGfx;

uint16_t LoadLineResistanceSoc;

DpmDescriptor_t DpmDescriptor[PPCLK_COUNT];

typedef struct {

uint8_t VoltageMode;

uint8_t SnapToDiscrete;

uint8_t NumDiscreteLevels;

uint8_t padding;

LinearInt_t ConversionToAvfsClk;

typedef struct {

uint32_t m;

uint32_t b;

} LinearInt_t;

QuadraticInt_t SsCurve;

typedef struct {

uint32_t a;

uint32_t b;

uint32_t c;

} QuadraticInt_t;

} DpmDescriptor_t;

uint16_t FreqTableGfx [NUM_GFXCLK_DPM_LEVELS ];

uint16_t FreqTableVclk [NUM_VCLK_DPM_LEVELS ];

uint16_t FreqTableDclk [NUM_DCLK_DPM_LEVELS ];

uint16_t FreqTableEclk [NUM_ECLK_DPM_LEVELS ];

uint16_t FreqTableSocclk [NUM_SOCCLK_DPM_LEVELS ];

uint16_t FreqTableUclk [NUM_UCLK_DPM_LEVELS ];

uint16_t FreqTableFclk [NUM_FCLK_DPM_LEVELS ];

uint16_t FreqTableDcefclk [NUM_DCEFCLK_DPM_LEVELS ];

uint16_t FreqTableDispclk [NUM_DISPCLK_DPM_LEVELS ];

uint16_t FreqTablePixclk [NUM_PIXCLK_DPM_LEVELS ];

uint16_t FreqTablePhyclk [NUM_PHYCLK_DPM_LEVELS ];

uint16_t DcModeMaxFreq [PPCLK_COUNT ];

uint16_t Padding8_Clks;

uint16_t Mp0clkFreq [NUM_MP0CLK_DPM_LEVELS];

uint16_t Mp0DpmVoltage [NUM_MP0CLK_DPM_LEVELS];

uint16_t GfxclkFidle;

uint16_t GfxclkSlewRate;

uint16_t CksEnableFreq;

uint16_t Padding789;

QuadraticInt_t CksVoltageOffset;

typedef struct {

uint32_t a;

uint32_t b;

uint32_t c;

} QuadraticInt_t;

uint8_t Padding567[4];

uint16_t GfxclkDsMaxFreq;

uint8_t GfxclkSource;

uint8_t Padding456;

uint8_t LowestUclkReservedForUlv;

uint8_t Padding8_Uclk[3];

uint8_t PcieGenSpeed[NUM_LINK_LEVELS];

uint8_t PcieLaneCount[NUM_LINK_LEVELS];

uint16_t LclkFreq[NUM_LINK_LEVELS];

uint16_t EnableTdpm;

uint16_t TdpmHighHystTemperature;

uint16_t TdpmLowHystTemperature;

uint16_t GfxclkFreqHighTempLimit;

uint16_t FanStopTemp;

uint16_t FanStartTemp;

uint16_t FanGainEdge;

uint16_t FanGainHotspot;

uint16_t FanGainLiquid;

uint16_t FanGainVrGfx;

uint16_t FanGainVrSoc;

uint16_t FanGainPlx;

uint16_t FanGainHbm;

uint16_t FanPwmMin;

uint16_t FanAcousticLimitRpm;

uint16_t FanThrottlingRpm;

uint16_t FanMaximumRpm;

uint16_t FanTargetTemperature;

uint16_t FanTargetGfxclk;

uint8_t FanZeroRpmEnable;

uint8_t FanTachEdgePerRev;

int16_t FuzzyFan_ErrorSetDelta;

int16_t FuzzyFan_ErrorRateSetDelta;

int16_t FuzzyFan_PwmSetDelta;

uint16_t FuzzyFan_Reserved;

uint8_t OverrideAvfsGb[AVFS_VOLTAGE_COUNT];

uint8_t Padding8_Avfs[2];

QuadraticInt_t qAvfsGb[AVFS_VOLTAGE_COUNT];

typedef struct {

uint32_t a;

uint32_t b;

uint32_t c;

} QuadraticInt_t;

DroopInt_t dBtcGbGfxCksOn;

typedef struct {

uint32_t a;

uint32_t b;

uint32_t c;

} DroopInt_t;

DroopInt_t dBtcGbGfxCksOff;

typedef struct {

uint32_t a;

uint32_t b;

uint32_t c;

} DroopInt_t;

DroopInt_t dBtcGbGfxAfll;

typedef struct {

uint32_t a;

uint32_t b;

uint32_t c;

} DroopInt_t;

DroopInt_t dBtcGbSoc;

typedef struct {

uint32_t a;

uint32_t b;

uint32_t c;

} DroopInt_t;

LinearInt_t qAgingGb[AVFS_VOLTAGE_COUNT];

typedef struct {

uint32_t m;

uint32_t b;

} LinearInt_t;

QuadraticInt_t qStaticVoltageOffset[AVFS_VOLTAGE_COUNT];

typedef struct {

uint32_t a;

uint32_t b;

uint32_t c;

} QuadraticInt_t;

uint16_t DcTol[AVFS_VOLTAGE_COUNT];

uint8_t DcBtcEnabled[AVFS_VOLTAGE_COUNT];

uint8_t Padding8_GfxBtc[2];

int16_t DcBtcMin[AVFS_VOLTAGE_COUNT];

uint16_t DcBtcMax[AVFS_VOLTAGE_COUNT];

uint8_t XgmiLinkSpeed [NUM_XGMI_LEVELS];

uint8_t XgmiLinkWidth [NUM_XGMI_LEVELS];

uint16_t XgmiFclkFreq [NUM_XGMI_LEVELS];

uint16_t XgmiUclkFreq [NUM_XGMI_LEVELS];

uint16_t XgmiSocclkFreq [NUM_XGMI_LEVELS];

uint16_t XgmiSocVoltage [NUM_XGMI_LEVELS];

uint32_t DebugOverrides;

QuadraticInt_t ReservedEquation0;

typedef struct {

uint32_t a;

uint32_t b;

uint32_t c;

} QuadraticInt_t;

QuadraticInt_t ReservedEquation1;

typedef struct {

uint32_t a;

uint32_t b;

uint32_t c;

} QuadraticInt_t;

QuadraticInt_t ReservedEquation2;

typedef struct {

uint32_t a;

uint32_t b;

uint32_t c;

} QuadraticInt_t;

QuadraticInt_t ReservedEquation3;

typedef struct {

uint32_t a;

uint32_t b;

uint32_t c;

} QuadraticInt_t;

uint16_t MinVoltageUlvGfx;

uint16_t MinVoltageUlvSoc;

uint16_t MGpuFanBoostLimitRpm;

uint16_t padding16_Fan;

uint16_t FanGainVrMem0;

uint16_t FanGainVrMem1;

uint16_t DcBtcGb[AVFS_VOLTAGE_COUNT];

uint32_t Reserved[11];

uint32_t Padding32[3];

uint16_t MaxVoltageStepGfx;

uint16_t MaxVoltageStepSoc;

uint8_t VddGfxVrMapping;

uint8_t VddSocVrMapping;

uint8_t VddMem0VrMapping;

uint8_t VddMem1VrMapping;

uint8_t GfxUlvPhaseSheddingMask;

uint8_t SocUlvPhaseSheddingMask;

uint8_t ExternalSensorPresent;

uint8_t Padding8_V;

uint16_t GfxMaxCurrent;

int8_t GfxOffset;

uint8_t Padding_TelemetryGfx;

uint16_t SocMaxCurrent;

int8_t SocOffset;

uint8_t Padding_TelemetrySoc;

uint16_t Mem0MaxCurrent;

int8_t Mem0Offset;

uint8_t Padding_TelemetryMem0;

uint16_t Mem1MaxCurrent;

int8_t Mem1Offset;

uint8_t Padding_TelemetryMem1;

uint8_t AcDcGpio;

uint8_t AcDcPolarity;

uint8_t VR0HotGpio;

uint8_t VR0HotPolarity;

uint8_t VR1HotGpio;

uint8_t VR1HotPolarity;

uint8_t Padding1;

uint8_t Padding2;

uint8_t LedPin0;

uint8_t LedPin1;

uint8_t LedPin2;

uint8_t padding8_4;

uint8_t PllGfxclkSpreadEnabled;

uint8_t PllGfxclkSpreadPercent;

uint16_t PllGfxclkSpreadFreq;

uint8_t UclkSpreadEnabled;

uint8_t UclkSpreadPercent;

uint16_t UclkSpreadFreq;

uint8_t FclkSpreadEnabled;

uint8_t FclkSpreadPercent;

uint16_t FclkSpreadFreq;

uint8_t FllGfxclkSpreadEnabled;

uint8_t FllGfxclkSpreadPercent;

uint16_t FllGfxclkSpreadFreq;

I2cControllerConfig_t I2cControllers[I2C_CONTROLLER_NAME_COUNT];

typedef struct {

uint32_t Enabled;

uint32_t SlaveAddress;

uint32_t ControllerPort;

uint32_t ControllerName;

uint32_t ThermalThrottler;

uint32_t I2cProtocol;

uint32_t I2cSpeed;

} I2cControllerConfig_t;

uint32_t BoardReserved[10];

uint32_t MmHubPadding[8];

} PPTable_t;

评论

肯定啊,它就是enio啊

这个好啊,是不是每次装驱动都会被重置要从新导入

评论

A卡有开箱即用的Linux开源驱动就是好

评论

CHH评测用的平台是7700K,跑分明显偏低的,我用9900K平台跑的分数要高很多了,这才是闪电的真正实力

评论

soft_pp,玩A卡的基本操作,不要惊讶

看我的表情,280%

评论

你的VEGA BIOS修改器会不会连这个也能改

评论

蒽呐,但是导入很简单啊,只要有大佬能看懂数据结构,会改那些奇怪的数字!

评论

你发的图显示显卡分数是17864,比评测的低一点,评测的显卡分数是17969。VII是16020和17753。

评论

女神妮怎么换头像了!

评论

突然意识到原来妳也有签名!不玩了不玩了!这个破论坛!

评论

你被针对了。

评论

我方主要看显卡得分。不是总分

评论

妮要写什么,我帮妮放

评论

那人家要放小剧场的介绍图片和链接,可以咩?

评论

彳亍口巴

m.jpg (4.01 KB, 下载次数: 0)

评论

不是我的呀,那个vega bios editor还不完善。

不过不用他也能改。

这个是powerplay table,在bios表里面是裸露的十六进制可以直接改,为了方便,可以提取成注册表文件直接导入,e**o提供的链接里面有教程的。

之前VEGA64改FE的时候我上传了VEGA一些常用的soft_pp,包含我自己提取的VEGA FE 8G的用于还原

自己就可以改哦

评论

妮怎么也换头像了!

评论

这个卡未来会有超公版吗?

评论

我要跟上本区的潮流!

评论

我靠

评论

我还怀疑了半天都不敢说

你们太坏了早就知道了也不告诉我一声

评论

只有 她 才用粉底

评论

都说了好几个月了吧?你可能经常不上论坛了吧?没见你和正义讨论xxx了

评论

我这不是因为不可抗力掉线了两个月最近才被放出来吗

所以我大概是全论坛最后一个知道楼主就是爱你哦的人?

评论

好像是不会有了,出货量就没多少

评论

应该是的,最近enio动静不小啊

评论

minori倒闭了 电路 电子 维修 我现在把定影部分拆出来了。想换下滚,因为卡纸。但是我发现灯管挡住了。拆不了。不会拆。论坛里的高手拆解过吗? 评论 认真看,认真瞧。果然有收 电路 电子 维修 求创维42c08RD电路图 评论 电视的图纸很少见 评论 电视的图纸很少见 评论 创维的图纸你要说 版号,不然无能为力 评论 板号5800-p42ALM-0050 168P-P42CLM-01

·日本中文新闻 日本26年新成人预估仅109万 与去年并列历史第二低

·日本中文新闻 日本皇居新年参贺突发裸奔事件 男子涉公然猥亵被捕

·日本中文新闻 印度宣布超越日本成为全球第四大经济体

·日本留学生活 在熟悉的城市,遇見不一樣的感受

·日本留学生活 求购一些水电燃气话费等公共料金请求书

·日本华人网络交流 制造信息垃圾的产业,这种现象在日本尤其普遍。

·日本华人网络交流 美军入侵 委内瑞拉领空 并非零伤亡

·日本华人网络交流 年末采购食品,恰时间就能全半价。

·中文新闻 马丁·克鲁内斯 (Martin Clunes) 在新剧中变身休·爱德华兹 (Huw Edw

·中文新闻 当朋友们讲述他们对他们的阴谋感到震惊以及他们如何向他们隐